SEMICON Taiwan主辦的異質整合國際高峰論壇第二天議程,齊聚業界一線大廠,重點探討晶片技術、共同封裝光學(CPO)元件、光學引擎、基板和測試解決方案,以及高效能運算、高密度模組和先進散熱解決方案,滿足下一代AI運算需求。

異質整合高峰論壇匯集產業重量級講者陣容,由博通(Broadcom)光學系統副總裁Manish Mehta博士擔任開場Keynote講者,他以「突破I/O障礙:共同封裝光學和異質整合的下一個前沿」為題發表演講。緊接著,NVIDIA CPO工程資深總監Barak Freedman 博士,則以「CPO:從概念到商用化」為主題進行演講。下午場則由聯發科副總Kevin Hu博士以「先進異質封裝基礎原理」為題擔任Keynote講者。

其他議程演講廠商,還包括檢測設備廠Comet、無人載具技術公司雷虎科技、量測解決方案提供商Camtek、化學材料廠李長榮化學,以及超導量子積體電路開發商Rigetti Computing等多家業者,分別聚焦檢測、材料、封裝、量子運算等多元技術領域,展現異質整合生態系統的完整性。

垂直整合優勢 博通CPO技術已進入商用部署

博通Manish Mehta博士揭示了共封裝光學領域採取垂直整合技術路徑。他強調博通內部垂直整合能力涵蓋完整技術鏈,從核心ASIC、混合信號IC到光學元件製造,公司內部擁有磷化銦晶圓廠,專門製造為CPO應用設計的連續波雷射晶片。博通並與台積電、日月光、矽品等重要合作夥伴攜手開發先進封裝技術。

博通Tomahawk 5 Bailey 系列已成功進入客戶現場商用部署階段,採用八個6.4T光學引擎共封裝設計,總計提供51.2T光學頻寬,成為業界首款大規模量產的CPO解決方案。合作夥伴Micas Networks已宣布該系列CPO交換器系統進入量產階段。

Manish Mehta 博士表示,當前世代100G/lane技術已達商用化成熟度,下一世代200G/lane產品已於2025年5月正式發布,未來規劃中的400G/lane產品正在開發階段。博通認為CPO技術將從橫向擴展網路起步,累積可靠性經驗後進軍縱向擴展應用領域,預期CPO將成為大規模GPU集群的核心互連技術。

功耗最佳化驅動 NVIDIA期望創造CPO產業聯盟

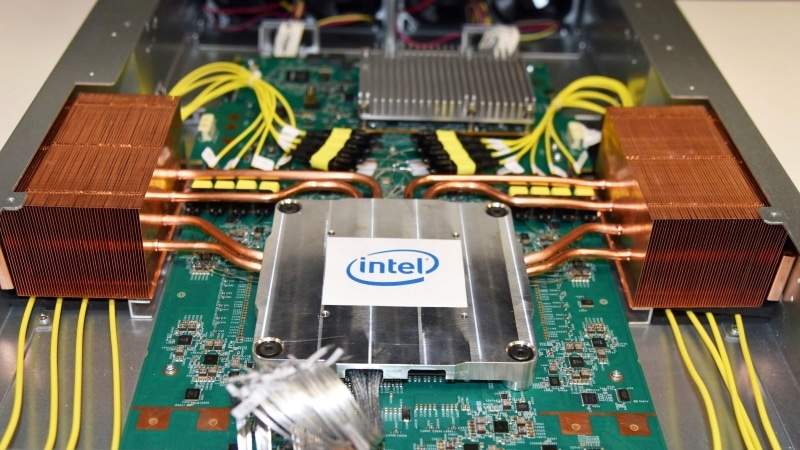

NVIDIA的Barak Freedman博士則是從AI工廠電力預算角度切入CPO技術需求,他強調CPO技術相較傳統方案可節省72%電力消耗,功耗降至原本的四分之一,節省的電力可重新分配給GPU運算使用,可實現系統級最佳化效益。

同時,他也強調NVIDIA與台積電在微環諧振器調製器(Micro Ring Resonator Modulator, MRM)矽光子引擎方面建立緊密合作關係,採用台積電COUPE緊湊型通用光子引擎製程技術,實現每波長200Gbps調變和超低密度設計。NVIDIA同時推動CPO連接器標準化進程,期望建立產業統一規範,共同應對矽光子晶片開發複雜性、封裝技術熱管理等技術挑戰。

CPO技術邁向成熟 異質整合開啟新競爭格局

博通和NVIDIA兩大技術巨頭的精彩演講,標誌著CPO技術從概念研發階段正式邁向商用化部署。博通強調垂直整合製造能力,NVIDIA則突顯系統級功耗最佳化,兩家公司不同的技術路徑展現CPO領域的多元發展可能性。同時,各家業者也在產業鏈上下游不斷深化合作,台灣廠商在先進封裝、檢測設備領域扮演關鍵支撐角色。

隨著AI算力需求持續爆發,異質整合技術將重塑AI時代的半導體競爭格局,CPO技術有望成為連接百萬GPU規模AI工廠的核心基礎設施。